논리 게이트(논리 회로)

논리게이트란

불 대수(bool algebra : 0(거짓)과 1(참) 2가지 값만을 처리하고 컴퓨터 스스템의 전기적인 논리회로의 상태와 서로 대응되는 성질을 가진다.)를 물리적 장치에 구현한 것으로

하나 이상의 논리적 입력값에 대해 논리 연산을 수행하여 하나의 논리적 출력값을 얻는 전자회로를 말한다.

AND, OR, NOT의 기본 불 대수를 수행하며, 이 기본 불 대수들의 결합으로 복합적인 논리 기능을 수행한다.

마치 배관공이 기성 제품들을 복잡한 배관으로 연결해 수도 시스템을 만드는 것처럼

논리 게이트를 사용하면 하드웨어 설계자가 밑바닥부터 모든 회로를 설계할 필요 없이

IC(직접회로)를 선으로 연결해 복잡한 회로를 쉽게 만들 수 있었다.

인버터(NOT을 수행하는 게이트) 기호에서 중요한 부분은 O(동그라미)다. 동그라미가 없는 삼각형은 버퍼(buffer)라고 하며, 버퍼는 단지 입력을 출력으로 전달하기만 한다.

인버터기호는 인버터를 다른 논리게이트와 별도로 독립적으로 사용할 때만 쓰인다.

즉, 인버터는 입력을 반전시켜서 출력한다는 말이다.

AND나 OR게이트가 가장 효육적인 게이트는 아니다.

트랜지스터-트랜지스터 논리(TTL)든 CMOS논 리든 논리게이트든 논리 게이트에서 가장 단순한 회로는 NAND나 NOR이다.

그 이유는 NAND나 NOR는 트랜지스터 2개(TTL)나 4개(CMOS) 사용한다.

반면 AND나 OR은 NAND나 NOR회로 출력에 트랜지스터를(반도체를 이용하여 전자 신호 및 전력을 증폭하거나 스위칭하는 데 사용되는 반도체소자) 덧붙여서 출력을 반전시켜야 하기 때문에 더 비싸고 반응 속도도 더 느리며, 전력도 더 많이 소모된다.

따라서 보통 디지털 회로 설계 시 가장 기본적으로 사용하는 게이트는 NAND나 NOR 게이트다.

드모르간의 법칙에 의해 NAND는 OR의 두 입력을 반전시킨 것과 같으므로 위 그림처럼

NAND 게이트를 OR 게이트로 쉽게 바꿔 그릴 수 있다.

이것은 NAND로 만든 인버터를 사용해 입력을 반전시켜서 OR를 만들었다.

NAND만 있으면 입출력에 NAND로 만든 인버터를 잘 활용하면 OR, AND, NOT 으로 표현할 수 있는 모든 논리를 표현할 수 있다.

이력 현상을 활용한 잡음 내성 향상

논리신호가 0에서 1로, 1에서 0 으로 순간적으로 바뀐다고 생각하기 쉽다

대부분의 경우, 특히 게이트를 서로 연결하는 경우에는 이 가정이 옳다

하지만 현실에서 사용 중인 신호 중에는 천천히 변하는 신호가 많다.

만약 신호가 천천히 변하게 되면 어떻게 될까?

왼쪽 그림의 입력은 조용하며 잡음이 없지만, 오른쪽 그림의 입력 신호에는 잡음이 있다.

잡음으로 인해 입력 신호가 문턱값을 여러 번 오락가락하기 때문에 출력 신호에 글리치(glitch : 작은 오류라는 뜻)가 생긴다.

이런 글리치를 이력 현상을 사용해 방지할 수 있다.

이력 현상이란 말을 판정기준이 이력(과거에 벌어진 일)에 따라 달라진다는 뜻이다.

위 그림에 있는 전이 함수는 대칭적이지 않다. 화살표로 표시해놓은 것처럼 올라가는 신호(0에서 1로 가는 신호)와 내려간는 신호(1에서 0으로 가는 신호)에 대한 전이 함수가 다르다. 출력이 0이면 오른쪽 곡선을 사용하고, 출력이 1이면 왼쪽 곡선을 사용한다.

이렇게 하면 올라가는 신호와 내려가는 신호에 대해 각기 다른 문턱값이 생긴다.

이 말은 입력 신호가 두 문턱값 중 하나를 넘어간 경우 반대쪽 문턱값을 지나가며 출력이 반전되려면 값이 상당히 많이 변해야 한다는 뜻이다. 따라서 잡음 내성이 더 커진다.

차동신호

잡음이 많아서 이력을 도입해도 충분하지 못한 경우가 있다.

차동이란 차이나는 격차라는 뜻이다

차동은 측정하는 값이 서로 반전관계인 신호 쌍의 차이를 측정하기 때문에 뭍은 이름이다.

0과 1을 경정하기 위해 측정하는 것은 상대적 위치 뿐이기 때문에 잡음이 있어도 영향을 미치지 못한다.

그러므로 차동신호를 도입한다

전파 지연

전파 지연은 입력의 변화가 출력에 영향을 미칠 때까지 걸리는 시간을 뜻한다.

전파 지연은 정확한 값은 아니고 제조 과정과 온도에 따라 생기는 편차와 게이트 출력에 도달하기까지 연결된 구성 부품의 수에 따라 결정되는 통계적인 측정값이다.

게이트에 최대 지연과 최소 지연이 있다. 실제 지연은 그 둘 사이의 어떤 값이다. 전파 지연은 논리 회로의 최대 속도를 제한하는 요소 중 하나이다.

회로 설계자들이 회로가 제대로 작동하기를 원한다면 최악의 경우에 해당하는 지연 시간을 가정해야한다.

즉, 최대 지연값과 최소 지연값을 감안해 설계를 수행해야 한다.

여러 게이트를 엮으면 회색 영역의 길이가 점점 더 길어진다.

출력유형

토템플 출력

일반 적인 게이트 출력이다.

트랜지스터가 토템폴(아메리카 인디언들이 세운 기둥 모양의 나무조각, 긴 통나무에 동물 위에 동물 같은 식으로 여러 형상을 조각함)처럼 세로로 나란히 늘어서 있어서 붙은 것이다.

그림을 보면 알 수 있지만 0인 출력을 1인 출력과 연결하면 음극과 양극을 서로 연결하는 것과 같은 일이 벌어지기 때문에 부품이 타버릴 수 도 있다.

오픈 컬렉터 출력

오픈 컬렉터/오픈 드레인 출력이 있다.

오픈 컬렉터/오픈 드레인은 여러개의 디바이스(장치)를 하나의 연결선으로

양방향 통신할 수 있도록 하는 회로 기술입니다.

또한, 오픈 컬렉터/오픈 드레인의 경우 레벨이 다른 디바이스에서도 Data 전송이 가능하기 때문에

레벨을 바꿀 때 쓰면 유용한 회로입니다.

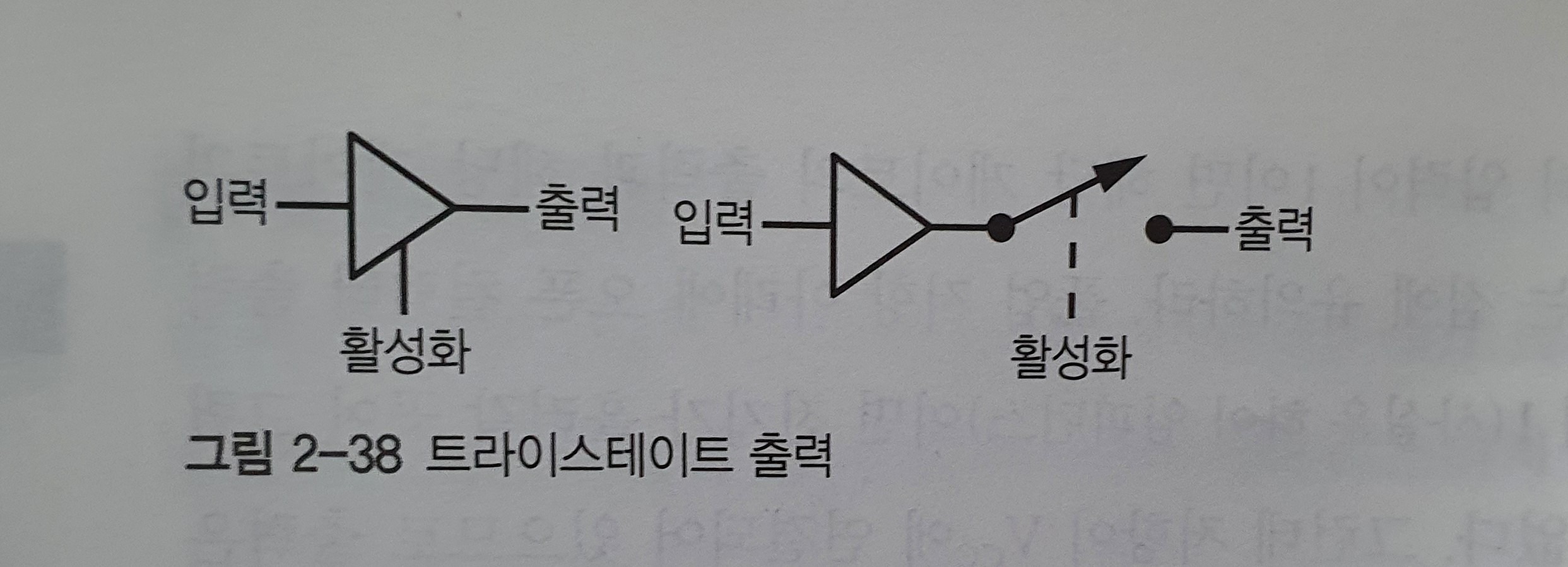

트라이스테이트 출력

논리회로에는 ‘Low’ 상태와 ‘High’ 상태 이외에 트라이 스테이트(Tri-State) 가 있다.

트라이 스테이트는 말 그대로 제3의 상태로서 ‘Low’ 상태로 도 ‘High’ 상태로도 정해져 있지 않고 출력 제어용 입력(Enable Input) 이 가해질 경우에만 입력 상태에 따라 정해지는 상태를 의미한다.

트라이 스테이트 출력을 사용하면 수많은 장치를 서로 선으로 직접 연결할 수 있다. 단점은 한 번에 단 하나의 장치만 활성화해야 한다는 점이다.

자료 출처

https://sites.google.com/site/hardbugss/hamkke-gongbuhagi

https://eunkyovely.tistory.com/30

https://m.blog.naver.com/PostView.naver?isHttpsRedirect=true&blogId=cni1577&logNo=221563118804